超大规模集成电路设计之基石 深入解析MOS器件原理(三)——从器件到集成电路设计的桥梁

在超大规模集成电路的设计体系中,对金属-氧化物-半导体场效应晶体管原理的深刻理解,是连接半导体物理与复杂电路、系统架构之间的核心桥梁。本部分将重点探讨MOS器件特性如何直接塑造并指导集成电路的设计实践。

一、器件特性对电路性能的直接影响

集成电路设计的起点,往往是对其基本构成单元——MOS管性能的精准把握。关键器件参数直接决定了电路的各项核心指标:

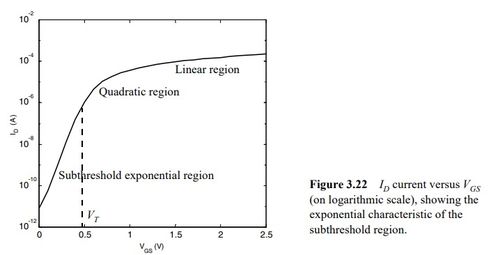

- 阈值电压(Vth):是决定电路工作电压、静态功耗和噪声容限的关键。低阈值电压器件有助于实现高速和低电压操作,但会加剧亚阈值漏电;高阈值电压器件则有利于降低静态功耗。现代设计常采用多阈值电压工艺,在关键路径使用低Vth器件提速度,在非关键路径使用高Vth器件控功耗。

- 跨导(gm)与输出阻抗(ro):晶体管的跨导直接决定了放大器的增益、驱动能力和速度(gm/C负载)。输出阻抗则影响放大器的本征增益(gm*ro)和电流源的理想度。模拟电路设计尤其需要精心偏置,以使器件工作在其高增益、高线性的区域。

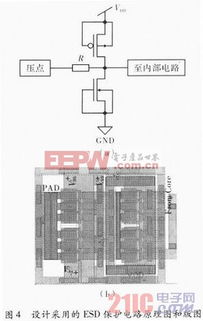

- 寄生电容与电阻:栅电容、结电容、覆盖电容等是决定电路速度(延迟~RC)的瓶颈。互联电阻和接触电阻则带来额外的RC延迟和信号完整性挑战。在超深亚微米工艺下,互连延迟已超过门延迟,成为主导因素,这迫使设计方法学从“逻辑驱动”转向“互连驱动”。

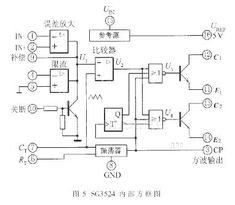

二、从器件物理到电路模型:SPICE模型的核心地位

集成电路设计并非直接操作物理器件,而是依赖于其数学模型——SPICE模型。模型精确地将器件的复杂物理行为(如短沟道效应、漏致势垒降低、迁移率退化、热载流子效应等)转化为设计工具可计算的电流、电容方程。模型的精度直接决定了设计仿真的可信度。一个成熟的集成电路设计流程,严重依赖于工艺厂提供的、经过硅验证的精确模型库,以确保流片前仿真与流片后测试结果的一致性。

三、缩放定律与设计挑战的演变

摩尔定律驱动下的器件等比例缩放,是超大规模集成电路发展的引擎。进入纳米尺度后,传统的缩放规则已部分失效,带来一系列设计挑战:

- 功耗危机:动态功耗(αCV²f)随电压降低而改善,但阈值电压无法等比例降低,导致静态亚阈值漏电流指数级增长。功耗密度成为限制芯片性能提升的主要瓶颈,催生了多核架构、动态电压频率调节、电源门控等系统级低功耗设计技术。

- 工艺变异与可靠性:器件尺寸的微小波动(如线边缘粗糙度)、掺杂随机涨落等,导致晶体管参数(如Vth)在芯片内和批次间出现显著统计性变异。这使得设计必须从追求“最优性能”转向保证“可制造性”和“良率”,广泛采用统计静态时序分析、可容忍变异的设计技术。

- 新型器件与电路协同优化:为应对传统平面MOSFET的物理极限,业界引入了如FinFET、GAA等三维器件结构。这些新结构具有更好的栅控能力和更低的漏电,但其不对称的寄生参数、复杂的制造工艺,也要求电路设计(特别是标准单元库、存储单元、IO电路)进行全新的优化和适配。

四、设计实例:器件原理在电路中的体现

以一个最基本的反相器为例:其开关速度、噪声容限、功耗全部由其负载管和驱动管的尺寸比(W/L)、阈值电压以及工艺参数决定。通过调整这个比例,可以在速度、功耗和面积之间进行权衡。在更复杂的电路如SRAM存储单元中,六个晶体管之间的尺寸比例需要极其精密的匹配,以确保足够的静态噪声容限和读写稳定性,这直接源于对晶体管在亚阈值区、线性区、饱和区行为的精确控制。

MOS器件原理绝非停留在教科书上的孤立知识。在超大规模集成电路设计中,它是进行性能预估、功耗分析、可靠性保障和新技术评估的根本语言。从晶体管的电流方程,到数亿门级芯片的系统规范,其间贯穿着一条由器件物理所定义的设计约束与可能性边界。唯有深入理解并尊重这些物理原理,设计者才能在日益复杂的工艺与系统需求中,创造出高效、可靠、创新的集成电路产品。后续的讨论将更深入地进入电路模块与系统架构的设计领域,而器件原理将始终是其不可或缺的底层支撑。