基于CMOS多功能数字芯片的ESD保护电路设计

随着集成电路工艺的不断进步,CMOS工艺因其低功耗、高集成度等优势,已成为数字芯片设计的主流技术。芯片特征尺寸的持续缩小导致栅氧化层越来越薄,使得芯片对静电放电(ESD)事件变得异常敏感。ESD事件可以在极短的时间内产生高达数千伏的电压和数安培的电流,对芯片造成永久性损伤,导致功能失效或可靠性下降。因此,在CMOS多功能数字芯片的设计中,集成高效、可靠的片上ESD保护电路已成为不可或缺的关键环节。

本文旨在探讨基于CMOS工艺的多功能数字芯片中ESD保护电路的设计原理、常用结构及设计考量。

一、 ESD保护电路的基本原理与设计目标

ESD保护电路的核心功能是为芯片内部脆弱的核心电路提供一个低阻抗的放电通路,在ESD事件发生时,能够迅速开启,将ESD电流安全地泄放到电源或地线,同时将内部节点的电压钳位在安全水平以下。一个优秀的ESD保护电路设计需满足以下几个关键目标:

- 低触发电压:确保在内部电路受损前,保护电路能抢先开启。

- 低钳位电压:在泄放ESD大电流时,其两端的压降(钳位电压)必须足够低,以保证内部节点电压不超过其击穿极限。

- 高电流泄放能力:能够承受ESD标准(如人体模型HBM、机器模型MM、充电器件模型CDM)所规定的电流冲击而不失效。

- 低泄漏电流:在正常工作状态下(非ESD事件),保护电路自身的漏电流必须极小,以避免增加芯片的静态功耗。

- 快速响应:对ns级的ESD脉冲能够快速响应。

- 面积效率:在满足性能的前提下,占用尽可能小的芯片面积。

二、 常用的CMOS ESD保护器件与电路结构

在CMOS工艺中,有多种器件可用于构建ESD保护电路,设计者常根据芯片的I/O类型、电源域和工艺特性进行选择和组合。

- 栅接地NMOS(GGNMOS):这是最经典且应用广泛的ESD保护器件。其利用NMOS晶体管的寄生双极型晶体管(NPN)效应来泄放电流。在ESD应力的正脉冲下,漏极与衬底之间的反偏PN结发生雪崩击穿,产生的空穴电流流经衬底电阻,抬高了源极-衬底结的电压,从而正向偏置并开启寄生NPN晶体管,形成低阻抗通路。其设计关键在于优化漏极扩散区的尺寸、接触孔间距以及衬底接触的布局,以降低寄生电阻,改善电流均匀性。

- 硅控整流器(SCR):SCR结构具有非常高的单位面积电流泄放能力和极低的钳位电压(接近维持电压),是面积效率极高的ESD保护器件。但其触发电压通常较高,且存在闩锁风险。因此,常通过改进结构(如低电压触发SCR, LVTSCR)或与其他器件(如GGNMOS)级联,来降低触发电压并防止误开启。

- 二极管:利用正向导通的二极管或反向击穿的齐纳二极管作为ESD保护元件。二极管串常用于电源钳位电路和不同电源域之间的ESD保护。其优点是响应快、电容小,但反向击穿二极管的触发电压受工艺影响较大。

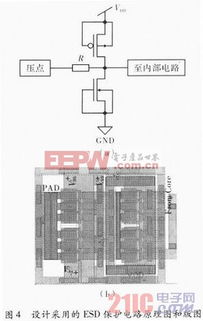

- 基于RC触发的电源钳位电路:这是保护电源引脚(VDD)和地引脚(VSS)之间核心电路的关键。它通常由一个RC网络、一个反相器和一个大的NMOS或PMOS泄放晶体管组成。在正常上电过程中,RC时间常数使反相器输入保持低电平,泄放管关闭。当快速的ESD脉冲出现时,电容耦合使反相器输入瞬间变为高电平,从而开启泄放管,在VDD和VSS之间建立泄放通路。

三、 面向多功能数字芯片的ESD保护电路设计策略

对于集成了数字逻辑、存储器、模拟模块、高速接口(如DDR, USB)的多功能芯片,其ESD保护设计更为复杂,需要系统性的策略。

- 整体架构规划:需要建立分层次的ESD保护网络。第一级是在所有I/O焊盘和电源焊盘上放置主保护电路,用于吸收绝大部分ESD能量。第二级是在内部各功能模块的输入端放置次级保护电路(通常尺寸较小),用于进一步限制进入核心电路的电压,并与主保护电路协同工作。

- I/O接口的定制化设计:针对不同类型的I/O,需设计不同的保护电路。例如,高速I/O对寄生电容极为敏感,需采用低电容的二极管或专门优化的GGNMOS结构;而高压I/O(如用于驱动显示的接口)则需要能承受更高工作电压的保护器件。

- 多电源域管理:芯片内通常存在多个电压域(如核心电压1.2V, I/O电压3.3V)。必须在不同电源域之间设计ESD电流泄放路径,例如使用背对背二极管或域间电源钳位电路,防止ESD电流因找不到通路而损伤栅氧。

- 布局布线优化:ESD保护电路的版图设计至关重要。必须确保ESD电流路径宽而短,避免电流拥挤导致的局部过热。电源线和地线网络必须足够强壮(宽金属、多通孔),以承载ESD大电流。保护器件与I/O焊盘的连接应直接而紧密。

- ESD设计规则检查(DRC)与仿真验证:利用工艺厂提供的ESD设计规则进行物理验证。结合传输线脉冲(TLP)仿真和电路级仿真,在设计的早期评估保护电路的触发特性、钳位能力和 robustness。

四、 与展望

在深亚微米及纳米级CMOS工艺下,ESD保护电路设计面临着电源电压降低、栅氧可靠性余量减小、工艺变异增大等新挑战。未来的设计趋势将更加依赖于工艺与器件的协同优化(如使用硅化物阻挡层、高能注入等)、新型器件结构(如全硅化漏极、FinFET ESD器件)的探索,以及更加智能和自适应的保护方案。对于设计者而言,深入理解ESD失效机理、工艺特性,并采用系统化、定制化的设计方法,是确保CMOS多功能数字芯片在严峻的ESD环境下依然可靠工作的根本保证。

片上ESD保护电路是CMOS芯片可靠性的第一道防线。其设计不再是简单的“附加”模块,而是需要与芯片整体架构、工艺特性深度结合的核心设计环节,直接关系到产品的市场竞争力和长期可靠性。