中规模集成电路功能测试仪的系统设计与实现

随着半导体技术的飞速发展,集成电路(IC)已成为现代电子系统的核心。在研发、生产及维修环节,对集成电路,特别是中规模集成电路(MSI)进行快速、准确的功能测试至关重要。一款设计精良的中规模集成电路功能测试仪,能够有效保障芯片质量,提升生产效率,降低研发与维护成本。本文旨在探讨其核心设计理念、系统架构与关键技术。

一、 系统总体架构设计

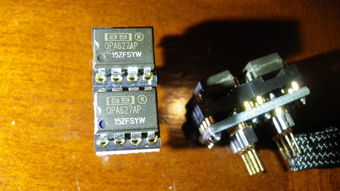

中规模集成电路功能测试仪是一种基于可编程控制的自动化测试设备。其核心设计目标是实现对多种型号、不同封装的MSI芯片进行功能验证。系统通常采用模块化设计,主要包括以下几个核心部分:

- 主控单元:作为系统大脑,通常由高性能微处理器(如ARM Cortex系列)或FPGA构成,负责执行测试程序、控制测试流程、处理数据并与上位机通信。

- 测试向量生成与施加模块:该模块根据被测芯片(DUT)的真值表或功能描述,生成相应的输入测试信号(测试向量),并通过精密的多路数字I/O通道施加到DUT的对应引脚。

- 响应采集与比较模块:同步采集DUT输出引脚的响应信号,并将其与预期的标准输出(“黄金向量”)进行实时比较,从而判断功能正确与否。

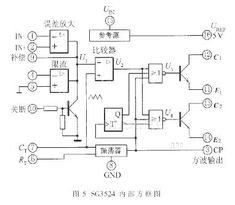

- 程控电源模块:为DUT提供稳定、可编程的电源电压(VCC/VDD)和参考电压,并能监测供电电流,以检测短路、开路或功耗异常。

- 适配器接口:设计灵活、可更换的测试插座或适配板,以兼容DIP、SOIC、PLCC等多种封装形式。

- 人机交互界面(HMI):通常为上位机软件,提供测试项目编辑、测试流程控制、结果显示(通过/失败)、数据记录与报表生成等功能。

二、 关键技术与设计要点

- 测试向量的高效生成与管理:测试向量的完备性和效率直接决定测试覆盖率。设计需支持从EDA工具导出测试向量,或提供图形化/脚本化编辑环境。采用向量压缩算法和循环执行机制,可以节省存储空间并提高测试速度。

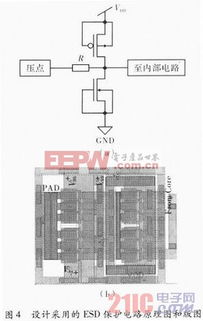

- 时序精确性与信号完整性:MSI芯片的工作频率可能达到数十至数百MHz,对测试信号的建立/保持时间、边沿速率、信号过冲等有严格要求。设计时需采用阻抗匹配、等长布线、去耦电容布局等信号完整性(SI)技术,并使用高性能驱动/缓冲芯片,确保测试信号的质量。

- 可编程数字I/O通道设计:这是系统的核心硬件。每个通道应具备独立的、驱动能力可调的驱动器和灵敏度可调的接收器(比较器)。通道状态(输入/输出/高阻)需可动态配置,以模拟复杂的总线交互场景。通道数量需足够覆盖目标MSI芯片的最大引脚数(通常为24-64脚)。

- 故障诊断与定位:功能测试仪不应仅给出“通过/失败”的二元结果。优秀的设计需支持故障诊断,例如通过“失效循环”定位到导致出错的特定测试向量,或通过多通道逻辑分析仪功能,捕获出错时刻前后的输入/输出波形,辅助工程师分析故障根源(如时序违例、竞争冒险等)。

- 系统校准与自检:为确保测试精度,仪器需具备自检和校准功能。例如,通过内部回环测试校准I/O通道的时序偏移,使用高精度万用表模块校准供电电压等。这保证了测试结果的长时期可靠性与可追溯性。

三、 软件系统设计

软件是发挥硬件效能的关键。测试仪软件通常分为下位机固件和上位机应用软件。

- 下位机固件:运行于主控单元,要求实时性高,负责底层硬件驱动、测试序列的高速执行、数据的实时采集与初步处理。

- 上位机软件:提供友好的图形用户界面,功能包括:

- 项目管理:创建、保存和加载针对不同芯片的测试项目。

- 测试编辑与调试:以波形图、真值表或高级语言(如类似C的脚本)形式编辑测试流程,支持单步、断点调试。

- 自动化测试:支持批量测试、条码扫描关联、测试结果自动分拣。

- 数据管理:将测试结果(包括序列号、测试时间、失效信息)存入数据库,并生成统计图表和测试报告。

四、 与展望

设计一款高性能的中规模集成电路功能测试仪,是一项涉及数字电路设计、模拟电路设计、信号完整性、嵌入式软件及上位机软件开发的综合性工程。其核心在于构建一个精准、灵活、可靠的“信号施加-响应比对”自动化平台。随着集成电路复杂度提升,测试仪将更加智能化,集成更多模拟/混合信号测试能力,并借助人工智能技术优化测试向量生成与故障诊断,向更高集成度的“片上系统(SoC)测试仪”方向演进,持续为集成电路产业保驾护航。