数字集成电路设计中的硬件加速验证技术 挑战、方法与未来趋势

在数字集成电路(IC)设计领域,随着工艺节点不断微缩、设计规模日益庞大以及功能复杂性急剧增加,传统的软件仿真验证方法已难以满足对验证效率和覆盖率的严苛要求。硬件加速验证技术,作为连接软件仿真与物理流片前硅前验证的关键桥梁,正成为确保芯片设计正确性、缩短产品上市周期的核心技术手段。本文将探讨硬件加速验证的技术内涵、主流实现方式、面临的挑战以及未来发展趋势。

一、硬件加速验证的技术内涵与价值

硬件加速验证的核心思想是利用专用的硬件平台(如FPGA、专用仿真器或原型验证系统)来执行设计的功能验证,其运行速度可比纯软件仿真快数个数量级。它允许设计团队在流片前,将大规模的数字设计映射到可编程硬件上,以接近真实硬件的速度运行完整的软件栈、操作系统及应用程序,从而进行系统级验证、性能评估和软硬件协同开发。这种技术显著加速了验证收敛过程,使团队能够更早地发现深层次的设计缺陷,并大幅降低因流片失败导致的成本风险。

二、主流硬件加速验证技术实现方式

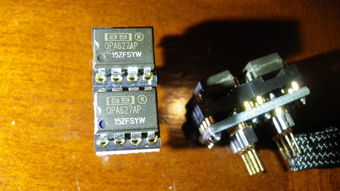

- 基于FPGA的原型验证:这是最广泛采用的硬件加速形式。设计团队将RTL代码综合并映射到多片FPGA构成的原型板上,搭建一个可实际运行的“虚拟芯片”。其优势在于成本相对较低、运行速度快(可达数十至数百MHz),且能直接连接真实的外设接口。它通常需要针对FPGA进行设计分区、时钟域处理以及存储器模型替换等额外工作。

- 专用硬件仿真器(Emulator):专用仿真器是由厂商提供的商业化大型系统,内含大量定制处理单元,专门用于加速仿真。它们通常提供完整的调试环境、自动化编译流程以及与软件仿真器的协同验证接口(如SCE-MI)。虽然购置成本高昂,但其处理能力极强,能够承载超大规模SoC设计,并提供优异的可控性和可观测性,特别适合复杂SoC的早期软件开发和系统验证。

- 混合验证平台:结合了软件仿真、硬件仿真和FPGA原型的优势。例如,将设计的关键模块或待验IP放入硬件加速器运行,而其余部分或测试平台仍在软件仿真环境中运行,通过高速通信接口进行数据交换。这种混合方式提供了灵活性与性能的平衡。

三、技术挑战与应对策略

尽管硬件加速验证优势明显,但其应用仍面临诸多挑战:

- 设计映射复杂性:将ASIC设计适配到FPGA架构需要解决资源差异、时钟网络、异步时序等问题。采用层次化原型设计和专用综合工具可以缓解这一困难。

- 调试能见度有限:硬件运行时内部信号的可观测性远不及软件仿真。解决方案包括嵌入在线逻辑分析仪(ILA)、采用可调试性设计(DFD)理念,以及利用仿真器的深度追踪功能。

- 编译时间过长:特别是对于大型设计,FPGA综合布局布线或仿真器的编译可能需要数小时甚至数天。增量编译、分区编译以及云平台分布式编译能有效改善此问题。

- 验证环境与激励移植:需要将软件仿真的测试平台和激励适配到硬件平台。采用基于事务级的验证方法学(如UVM)和标准协同建模接口(如SCE-MI)有助于提升移植效率和复用性。

四、未来发展趋势

- 与云计算的深度融合:云平台提供弹性的、可扩展的硬件加速验证资源池,使中小企业也能以服务形式使用高端仿真器,并支持大规模并行验证任务。

- 人工智能/机器学习的赋能:AI技术可用于优化验证激励生成、加速错误根因分析、预测编译结果,甚至智能管理验证资源与任务调度。

- 系统级与软硬件协同验证:随着Chiplet和异构集成技术的兴起,硬件加速验证平台将更侧重于系统级性能、功耗和互操作性验证,支持更早的软硬件集成与性能分析。

- 形式化验证与硬件加速的互补:形式化验证工具与硬件加速平台结合,能对特定属性进行 exhaustive 验证,而硬件加速则负责系统级动态场景验证,二者结合可构建更完备的验证流程。

硬件加速验证技术已成为现代数字集成电路设计流程中不可或缺的一环。它不仅是应对设计规模爆炸性增长的技术必然,也是实现芯片一次成功、抢占市场先机的战略支撑。随着技术不断演进与生态持续完善,硬件加速验证将与云计算、人工智能等前沿技术更紧密地结合,为集成电路设计创新提供更强大、更智能的验证引擎。