静态时序分析在数字集成电路设计中的关键作用与应用

在数字集成电路设计流程中,静态时序分析扮演着至关重要的角色。它是一种通过分析电路拓扑结构和时序约束,在不依赖仿真测试向量的情况下,验证电路在所有可能工作条件下是否满足时序要求的方法。与动态时序仿真相比,STA具有速度快、覆盖全面的显著优势,已成为现代超大规模集成电路设计签核阶段不可或缺的一环。

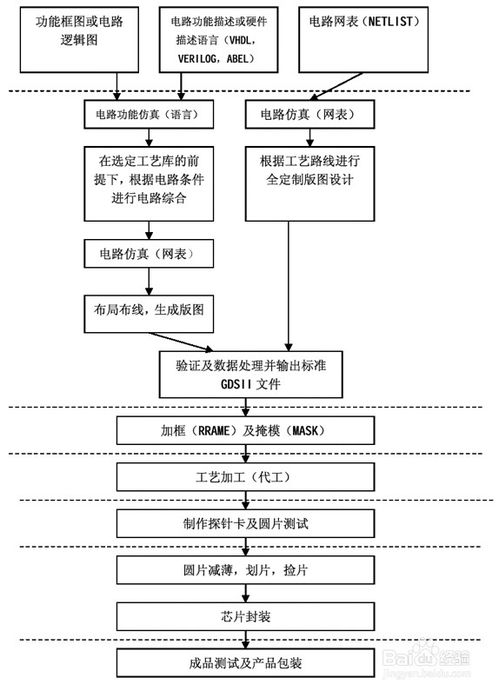

静态时序分析的核心应用贯穿于设计流程的多个阶段。在逻辑综合阶段,设计工具利用STA来评估和优化组合逻辑与时序路径,确保初步网表满足建立时间和保持时间的要求。在布局布线阶段,STA则用于分析由互连线寄生电阻电容引入的延迟,指导工具进行时序驱动的布局优化与时钟树综合。到了最后的签核验证阶段,基于最坏情况工艺角的STA更是确保芯片能在各种PVT条件下可靠工作的最终保障。

具体而言,STA通过构建时序图,计算信号从起点到终点的所有路径延迟。它重点关注建立时间检查和保持时间检查这两类最基本的时序约束。建立时间检查确保数据在时钟有效沿到来之前已稳定到达寄存器;而保持时间检查则确保数据在时钟有效沿之后能维持足够时间不被新数据覆盖。通过分析所有寄存器之间的路径,STA能够精确地报告出时序违规点,为设计者提供明确的优化方向。

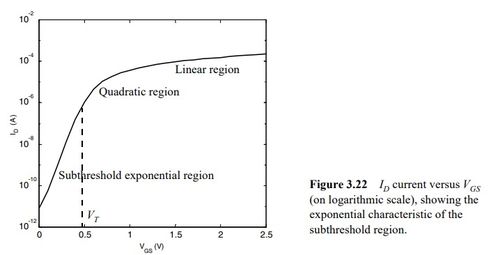

在深亚微米及纳米工艺节点下,互连线延迟已超过门延迟成为主要因素,同时工艺变异、串扰、电压降等效应日益显著。现代STA工具已集成噪声分析、功耗感知时序分析等高级功能,能够更精确地建模这些复杂效应。片上变异分析、统计静态时序分析等方法的出现,使设计者能够在考虑工艺随机性的情况下仍能保证芯片良率。

总而言之,静态时序分析是连接数字集成电路设计前端与后端、理想与物理实现的关键桥梁。它通过严谨的数学方法,为高速、高复杂度芯片的时序收敛提供了高效、可靠的分析手段。随着集成电路向更高性能、更低功耗方向不断发展,STA的方法与工具也必将持续演进,继续支撑着摩尔定律向前迈进。

最新产品